Frequency Response Analysis of Common Source MOSFET Amplifier

Aim

- Using LTspice Software simulation.

- Hardware implementation on bread board.

Apparatus & Software

| Component | Quantity |

|---|---|

| Function Generator | 1 |

| DC Supply | 1 |

| Oscilloscope | 1 |

| MOSFET 2N7000 | 1 |

| Bread Board | 1 |

| Connecting Wires | - |

| 100 kΩ Resistor | 1 |

| 33 kΩ Resistor | 1 |

| 2.7 kΩ Resistor | 1 |

| 820 kΩ Resistor | 1 |

| 470 Ω Resistor | 1 |

| 1 µF Capacitor | 2 |

| 10 µF Capacitor | 1 |

Theory

- Cut-off region: VGS < Vt — No channel is formed; the device is OFF and ID ≈ 0.

- Linear (Triode) region: VGS > Vt and VDS < (VGS − Vt) — The channel exists throughout; the MOSFET acts like a voltage-controlled resistor.

- Saturation region: VGS > Vt and VDS > (VGS − Vt) — The channel is pinched off at the drain end. The drain current becomes approximately independent of VDS.

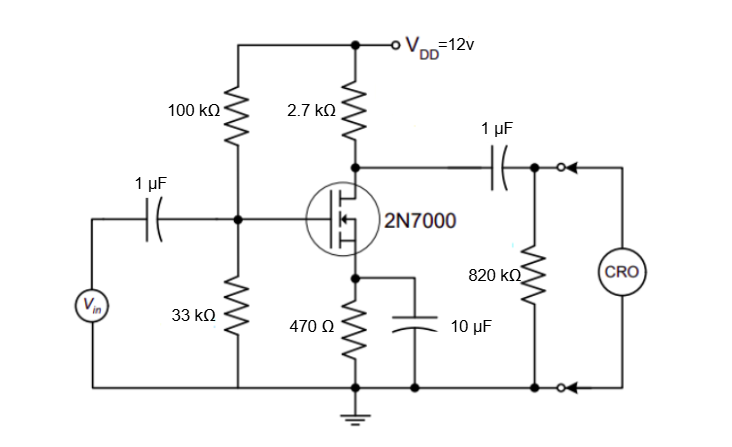

Pre-Lab / Circuit Diagram

Fig 1: Common Source MOSFET (2N7000) amplifier circuit with VDD = 12 V. R1 = 100 kΩ, R2 = 33 kΩ, RD = 2.7 kΩ, RS = 470 Ω, RL = 820 kΩ, Cin = Cout = 1 µF, CS = 10 µF.

Procedure

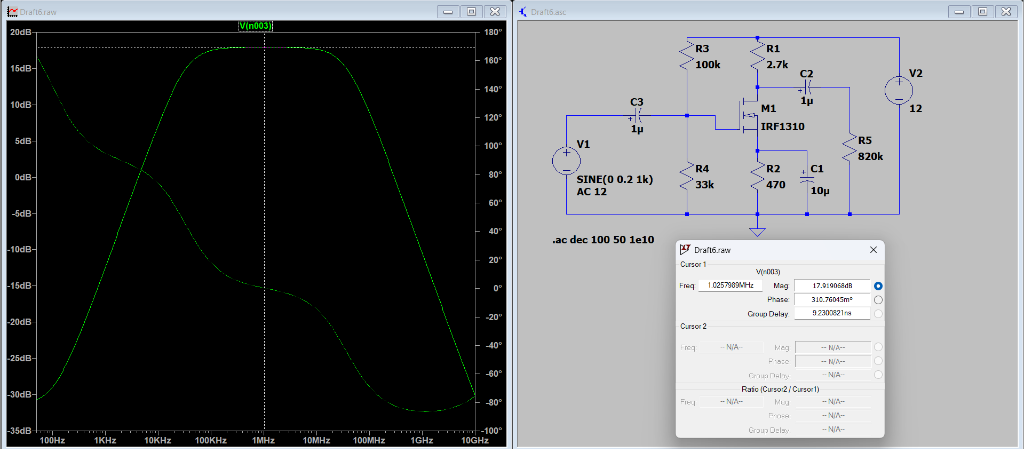

- Draw the CS amplifier schematic in LTspice using IRF1310 as an equivalent model for 2N7000 (2N7000 is unavailable in the LTspice library). Set VDD = 12 V, RD = 2.7 kΩ.

- Set the input signal source to SINE(0 0.2 1k) with AC amplitude 12 for the AC analysis.

- Set up an AC analysis directive: .ac dec 100 50 1e10 (decade sweep, 100 points/decade, from 50 Hz to 10 GHz).

- Run the simulation and plot V(out) in dB versus frequency to obtain the Bode plot.

- Use cursors to identify the peak mid-band gain, lower cutoff frequency (fL), and upper cutoff frequency (fH).

- Set up the circuit on a breadboard as per the circuit diagram: R1 = 100 kΩ, R2 = 33 kΩ, RD = 2.7 kΩ, RS = 470 Ω, RL = 820 kΩ, CC = 1 µF, CS = 10 µF, VDD = 12 V.

- Connect the function generator to the input (Vin) and the oscilloscope to both input and output terminals.

- Set the input signal to a sinusoidal wave at 1 kHz with an amplitude of 0.2 V.

- Vary the frequency of the input signal over a range of values (from 1 Hz to 2 MHz) and record the output voltage Vpp at each frequency step.

- Calculate the voltage gain and gain in dB at each frequency: Gain (dB) = 20 log₁₀(Vout / Vin).

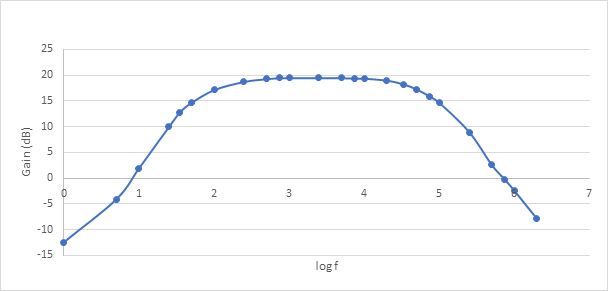

- Plot gain (dB) vs log(frequency) to obtain the Bode plot. Mark the mid-band gain and the high and low frequency −3 dB cutoff points.

Simulation / Execution

LTspice simulation — Peak gain identification: Cursor at 1.026 MHz shows peak gain of 17.92 dB. LTspice schematic uses IRF1310 (equivalent for 2N7000), with .ac dec 100 50 1e10 directive.

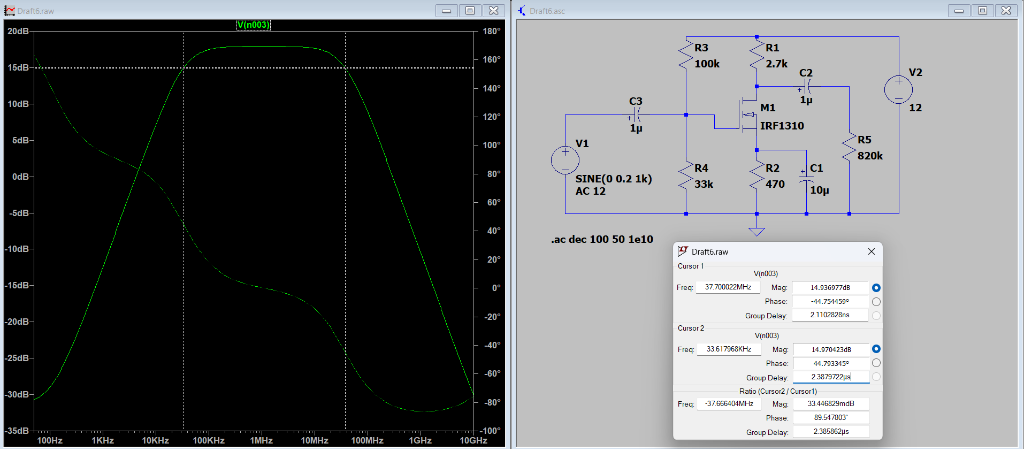

LTspice simulation — Bandwidth identification: Cursor 1 at fH = 37.7 MHz (gain = 14.94 dB); Cursor 2 at fL = 33.6 kHz (gain = 14.97 dB). Both ≈ 15 dB, confirming −3 dB points from peak of ~18 dB.

Observations

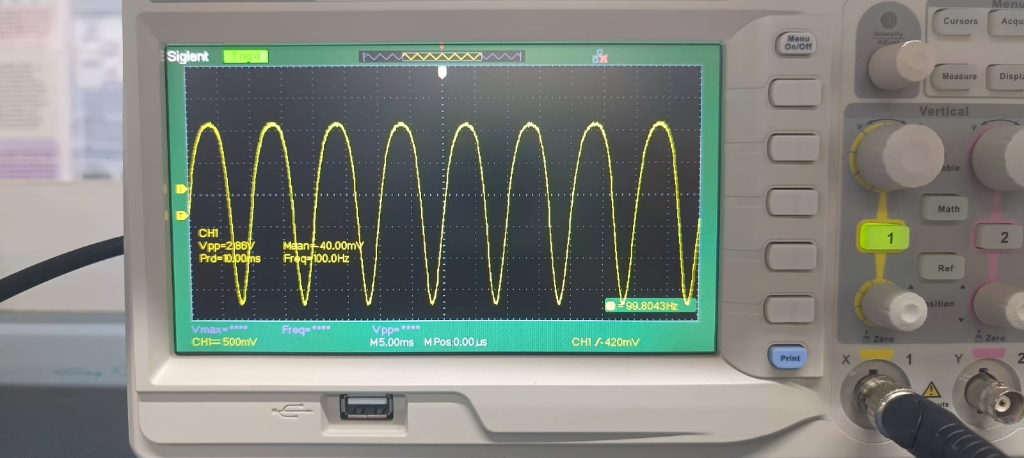

Oscilloscope — 100 Hz: Output Vpp = 2.88 V, Freq = 99.80 Hz. Low-frequency region — gain has not yet reached mid-band peak.

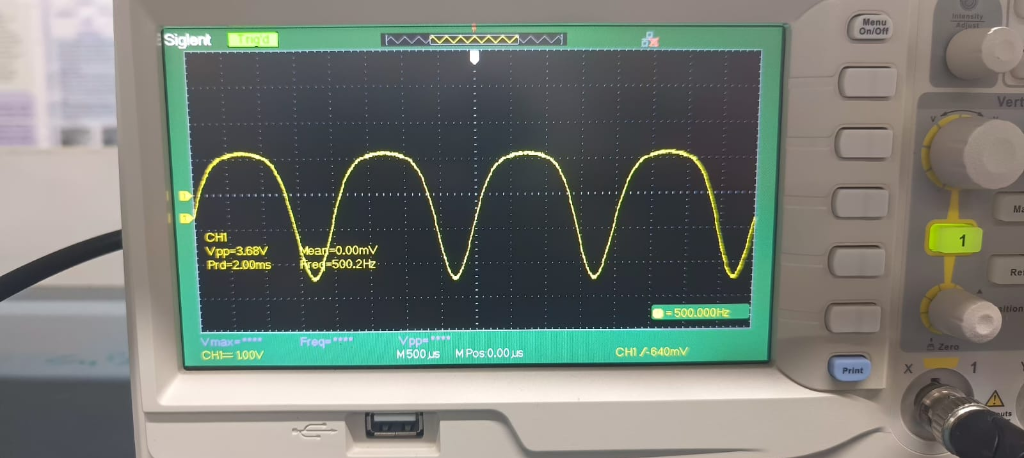

Oscilloscope — 500 Hz: Output Vpp = 3.68 V, Freq = 500.2 Hz. Near mid-band — gain approaching plateau.

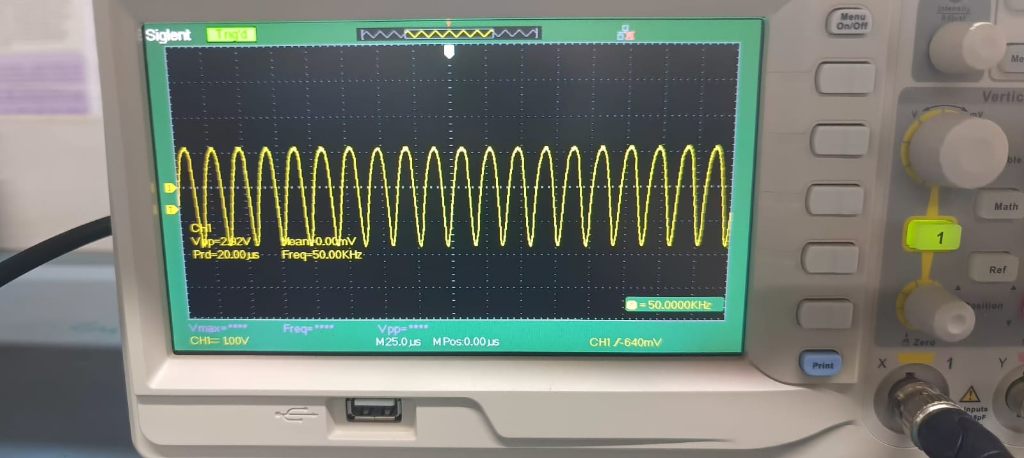

Oscilloscope — 50 kHz: Output Vpp = 2.92 V, Freq = 50 kHz. High-frequency region — gain has rolled off from mid-band peak.

| Frequency (Hz) | log f | Output Voltage Vpp (V) | Gain (dB) |

|---|---|---|---|

| 1 | 0 | 0.095 | -12.49 |

| 5 | 0.699 | 0.25 | -4.08 |

| 10 | 1 | 0.5 | 1.94 |

| 20 | 1.398 | 1.26 | 9.97 |

| 35 | 1.544 | 1.75 | 12.82 |

| 50 | 1.699 | 2.16 | 14.65 |

| 100 | 2 | 2.88 | 17.15 |

| 250 | 2.398 | 3.46 | 18.74 |

| 500 | 2.699 | 3.68 | 19.28 |

| 750 | 2.875 | 3.76 | 19.46 |

| 1000 | 3 | 3.76 | 19.46 |

| 2500 | 3.398 | 3.76 | 19.46 |

| 5000 | 3.699 | 3.76 | 19.46 |

| 7500 | 3.875 | 3.72 | 19.37 |

| 10000 | 4 | 3.72 | 19.37 |

| 20000 | 4.301 | 3.56 | 18.99 |

| 33000 | 4.519 | 3.28 | 18.28 |

| 50000 | 4.699 | 2.92 | 17.27 |

| 75000 | 4.875 | 2.48 | 15.85 |

| 100000 | 5 | 2.16 | 14.65 |

| 250000 | 5.398 | 1.12 | 8.94 |

| 500000 | 5.699 | 0.536 | 2.54 |

| 750000 | 5.875 | 0.384 | -0.35 |

| 1000000 | 6 | 0.3 | -2.50 |

| 2000000 | 6.301 | 0.16 | -7.96 |

Bode plot (hardware): Gain (dB) vs log(frequency). Peak mid-band gain ≈ 19.46 dB.

Calculations

Results & Analysis

| Parameter | Hardware (Measured) | LTspice Simulation |

|---|---|---|

| Mid-Band Gain (dB) | ≈ 19.46 dB | ≈ 17.92 dB |

| Lower Cutoff Frequency fL | ≈ 33 kHz | ≈ 33.6 kHz |

| Upper Cutoff Frequency fH | ≈ 750 kHz | ≈ 37.7 MHz |

| Bandwidth BW | ≈ 717 kHz | ≈ 37.7 MHz |

- The hardware and simulation results are in close agreement for mid-band gain (19.46 dB vs 17.92 dB) and lower cutoff frequency (~33 kHz in both).

- The upper cutoff frequency differs significantly: ~750 kHz (hardware) vs ~37.7 MHz (simulation). This is primarily due to the use of IRF1310 (a high-current power MOSFET with different parasitic capacitances) as a substitute for 2N7000 in LTspice, which does not accurately model the high-frequency behaviour of the 2N7000 signal MOSFET.

- The frequency response curve exhibits the expected band-pass shape with a well-defined flat gain region (mid-band) between 750 Hz and 7.5 kHz in hardware.

Conclusion

Post-Lab / Viva Voce

- Q: What is the role of the source bypass capacitor CS in a Common Source amplifier?

A: CS is connected in parallel with RS. At DC, CS is open, so RS provides bias stability through negative feedback. At AC signal frequencies, CS acts as a short circuit (impedance 1/ωCS ≈ 0), bypassing RS and eliminating AC signal degeneration. This maximises the AC voltage gain. Without CS, the gain would be reduced by the factor (1 + gm·RS), making CS essential for achieving high gain in the mid-band. - Q: What are the three operating regions of a MOSFET and which is used for amplification?

A: The three operating regions are: (1) Cut-off (VGS < Vt) — no channel, no current; (2) Linear/Triode (VGS > Vt, VDS < VGS − Vt) — MOSFET acts as a voltage-controlled resistor; (3) Saturation (VGS > Vt, VDS > VGS − Vt) — drain current is approximately constant, ID ≈ k'(VGS − Vt)². For amplification, the MOSFET must be biased in the saturation region, where the drain current is a smooth, approximately linear function of VGS, enabling large voltage gain. - Q: Why does the gain of a CS amplifier roll off at both low and high frequencies?

A: At low frequencies, coupling capacitors (Cin, Cout) and bypass capacitor CS have high impedance and do not fully pass or bypass signals, causing gain reduction. At high frequencies, internal parasitic capacitances of the MOSFET (Cgs, Cgd) create feedback and loading that limit bandwidth. The Miller effectmiller effectThe multiplication of an inverting amplifier's feedback capacitance by the voltage gain, making it appear much larger at the input. It limits high-frequency performance. due to Cgd amplifies the effective input capacitance as Cin,eff = Cgd(1 + |Av|), forming a low-pass filter with the source resistance and causing high-frequency gain roll-off. - Q: Define bandwidth and explain how it is measured from a Bode plot.

A: Bandwidth (BW = fH − fL) is the range of frequencies over which the gain remains within −3 dB of the mid-band value. On a Bode plot, fL and fH are identified as the frequencies where the gain curve crosses the mid-band gain minus 3 dB. A wider bandwidth means the amplifier faithfully amplifies a broader range of frequencies. In this experiment, the hardware BW ≈ 717 kHz and simulation BW ≈ 37.7 MHz. - Q: What is the voltage gain expression for a Common Source amplifier and what determines it?

A: The small-signal voltage gain is Av = −gm(RD ∥ RL). The negative sign indicates phase inversion. The magnitude depends on the transconductance gm = 2k'(VGS − Vt) = 2ID/(VGS − Vt), which is set by the Q-point, and the effective drain load (RD ∥ RL). Increasing RD or gm increases gain, but this is limited by the DC operating point — a larger RD reduces VDS and can push the MOSFET out of saturation. - Q: Why does the simulation result differ from the hardware measurement, particularly at high frequencies?

A: The primary reason is the use of IRF1310 as a substitute for the unavailable 2N7000 model in LTspice. The IRF1310 is a high-current power MOSFET with significantly different parasitic capacitances (Cgs, Cgd) compared to the 2N7000 signal MOSFET. This causes the simulated upper cutoff frequency (37.7 MHz) to differ greatly from the hardware value (~750 kHz). Additional factors include component tolerances, breadboard parasitic capacitance, and oscilloscope probe loading. - Q: What is the Miller effect and how does it impact the high-frequency response of a CS amplifier?

A: The Miller effect refers to the multiplication of the feedback capacitance Cgd (gate-drain capacitor) by the voltage gain, creating a large effective input capacitance: Cin,eff = Cgd(1 + |Av|). This large capacitance forms a low-pass RC filter with the signal source resistance, limiting the high-frequency response. As gain increases, the Miller capacitance increases proportionally, causing a lower upper cutoff frequency. This is a fundamental trade-off: higher gain amplifiers have a narrower bandwidth, captured in the gain-bandwidth product (GBW = Av × BW ≈ constant).

References & Resources (Not Applicable)

This section is not required for this experiment.

Was this experiment helpful?

Your feedback helps us improve

Please Sign In to rate this experiment.