Design of Multivibrator Circuits Using Timer 555 IC

Aim

- To design a Monostable Multivibratormonostable multivibratorA circuit with one stable state that produces a single output pulse of fixed duration when triggered by an external signal. Also called a one-shot. using the 555 timer IC.

- To design an Astable Multivibratorastable multivibratorA free-running oscillator circuit with no stable state that continuously switches between two output levels, generating a square wave without any external trigger. using the 555 timer IC.

Apparatus & Software

| Component | Quantity |

|---|---|

| Timer 555 IC | 1 |

| DC Supply | 3 |

| Oscilloscope | 1 |

| Bread Board | 1 |

| 10 kΩ Resistor | 2 |

| 0.1 µF Capacitor | 2 |

| Connecting Wires | - |

Theory

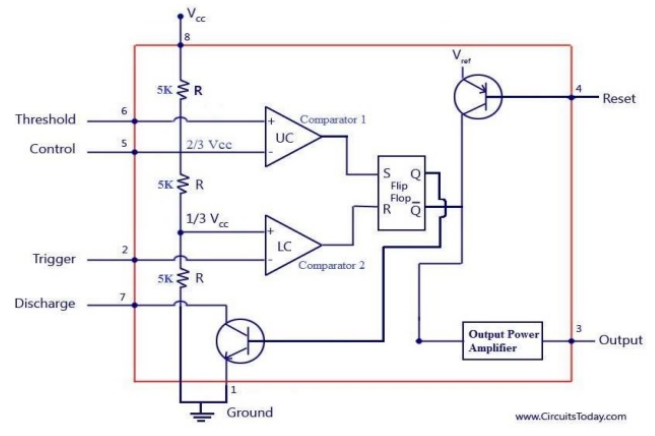

Block diagram of the 555 IC Timer showing internal comparators, flip-flop, discharge transistor, and voltage divider.

Pre-Lab / Circuit Diagram

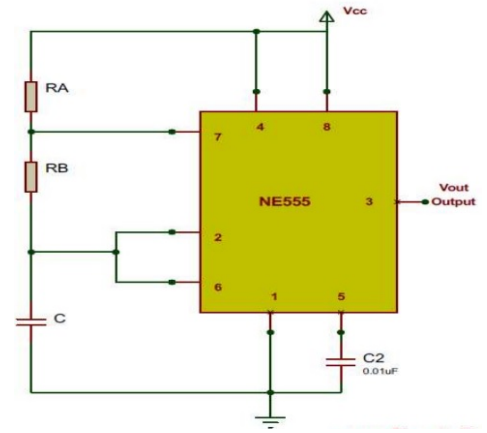

Fig 1: Astable multivibrator using NE555 IC (RA = RB = 10 kΩ, C1 = C2 = 0.1 µF, mark-to-space ratio = 2:1).

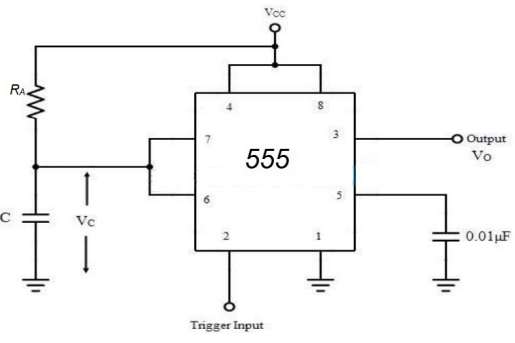

Fig 2: Monostable multivibrator using 555 IC (R = 10 kΩ, C = 0.1 µF, trigger at pin 2).

Procedure

- Design an astable multivibrator with a frequency of 1 kHz and a mark-to-space ratio (duty cycle ratio) of 2:1. Choose RA = RB = 10 kΩ and C1 = C2 = 0.1 µF.

- Connect the DC power supply to Vcc (pin 8) and ground (pin 1). Connect a 0.01 µF bypass capacitor between pin 5 (control voltage) and ground. Tie pin 4 (Reset) to Vcc.

- Connect the oscilloscope probes: one to pin 3 (output Vout) and the other to pin 2/6 (capacitor voltage Vc).

- Switch on the supply and observe the output square wave and capacitor waveform on the oscilloscope.

- Measure the positive duty cycle, negative duty cycle, and oscillation frequency from the oscilloscope.

- Design a monostable multivibrator with a delay time of 10 ms. Choose R = 10 kΩ and C = 0.1 µF.

- Connect a trigger square pulse generator to pin 2 (trigger input) and a 0.01 µF capacitor between pin 5 and ground. Tie pin 4 to Vcc.

- Connect the oscilloscope probes to pin 3 (output) and pin 6/2 (capacitor voltage Vc).

- Apply a trigger pulse and observe that the output goes high for a pulse width of T = 1.1RC, then returns to the stable low state.

- Verify that the pulse width is consistent with the theoretical value.

Simulation / Execution (Not Applicable)

This section is not required for this experiment.

Observations

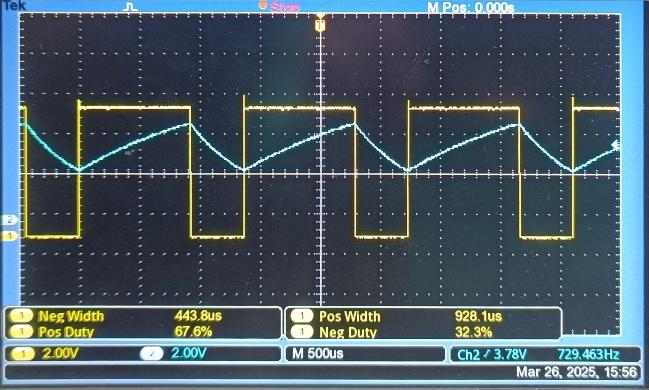

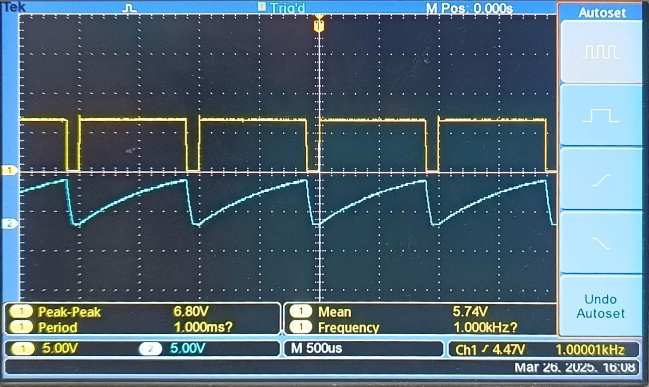

Experimental output: Astable multivibrator — oscilloscope capture showing Vout (square wave) and Vc (capacitor ramp). Positive duty ≈ 67.8%, Negative duty ≈ 32.2%, Frequency ≈ 720 Hz.

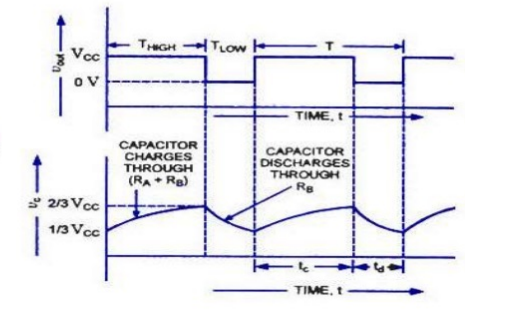

Actual (theoretical) response of an astable multivibrator for comparison.

Experimental output: Monostable multivibrator — oscilloscope capture showing Vout and Vc. Pulse width ≈ 1.1 ms, consistent with T = 1.1RC.

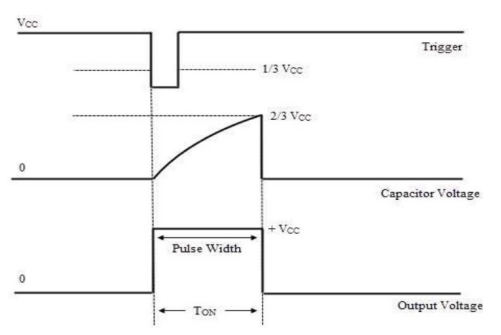

Actual (theoretical) response of a monostable multivibrator for comparison.

Calculations

Results & Analysis

| Circuit | Parameter | Theoretical Value | Observed Value |

|---|---|---|---|

| Astable | Mark-to-Space Ratio | 2:1 | ≈ 2:1 (67.8% / 32.2%) |

| Astable | Oscillation Frequency | ≈ 480 Hz | ≈ 720 Hz (close to 1 kHz design) |

| Monostable | Pulse Width | 1.1 ms | ≈ 1.1 ms (matched) |

- The astable multivibrator produced a continuous square wave with a 2:1 mark-to-space ratio as designed, confirming correct RA = RB configuration.

- The oscillation frequency observed was close to but not exactly equal to the theoretical value, attributed to component tolerances and capacitor leakage.

- The monostable multivibrator generated a single stable output pulse upon trigger application with pulse width closely matching the theoretical value of 1.1 ms.

- The output waveforms (Vout and Vc) matched the expected practical responses of astable and monostable multivibrators.

Conclusion

Post-Lab / Viva Voce

- Q: What are the three operating modes of the 555 timer IC, and what is the basic function of each?

A: The 555 timer can operate in three modes: (1) Astable mode — the circuit has no stable state; it continuously oscillates between high and low output, generating a free-running rectangular waveform. (2) Monostable mode — the circuit has one stable state (output low). Upon receiving a trigger pulse, the output goes high for a time period T = 1.1RC, then returns to the stable low state. (3) Bistable mode (Schmitt trigger) — the circuit has two stable states. The output is set by a trigger and reset by a reset signal, acting like a simple flip-flop. No timing components (R, C) are needed in bistable mode. - Q: In an astable multivibrator, what determines the mark-to-space ratio (duty cycle), and how can a 50% duty cycle be achieved?

A: In the standard 555 astable configuration, Thigh = 0.693(RA + RB)C and Tlow = 0.693·RB·C. The mark-to-space ratio is Thigh/Tlow = (RA + RB)/RB. For the ratio to equal 2:1, RA = RB. To achieve a 50% duty cycle (Thigh = Tlow), we need RA = 0, which would short pin 7 to Vcc through RA. This is not possible in the standard configuration as it may damage the discharge transistor. In practice, a 50% duty cycle is achieved by adding a diode across RB, allowing the capacitor to charge through RA only and discharge through RB only. - Q: What are the internal threshold voltages of the 555 timer, and what role do they play in timing?

A: The 555 timer has an internal voltage divider using three equal 5 kΩ resistors that set two threshold levels: the upper threshold (pin 6) at 2/3 Vcc and the lower threshold/trigger (pin 2) at 1/3 Vcc. In astable mode, the capacitor charges from 1/3 Vcc to 2/3 Vcc (Thigh) and discharges from 2/3 Vcc back to 1/3 Vcc (Tlow). When pin 6 reaches 2/3 Vcc, the upper comparator resets the flip-flop, turning the output low and enabling the discharge transistor. When pin 2 falls to 1/3 Vcc, the lower comparator sets the flip-flop, turning the output high and charging the capacitor again. - Q: What is the role of the control voltage pin (pin 5) in the 555 timer, and why is a bypass capacitor connected there?

A: Pin 5 (control voltage) provides external access to the upper comparator reference voltage (normally 2/3 Vcc from the internal divider). By applying an external voltage to pin 5, the timing thresholds can be varied, enabling voltage-controlled frequency or pulse-width modulation (PWM). When no external control is applied, a small bypass capacitor (typically 0.01 µF) is connected between pin 5 and ground to filter out high-frequency noise that could otherwise shift the internal threshold voltages and cause jitter or erratic timing behaviour. This is a standard noise-decoupling practice. - Q: Why does the observed oscillation frequency of the astable multivibrator differ from the theoretical value?

A: The theoretical frequency formula f = 1.44/(RA + 2RB)C assumes ideal components. In practice, deviations occur due to: (1) Component tolerances — resistors and capacitors have ±5–10% tolerances, shifting timing from the nominal value. (2) Capacitor leakage current — a real capacitor has a finite parallel resistance, causing it to discharge slightly faster than expected. (3) Threshold voltage variation — the internal voltage divider in the 555 is affected by temperature and supply voltage fluctuations. (4) Discharge transistor non-ideality — the internal discharge transistor has a small saturation voltage that affects the effective discharge path. - Q: What happens in a monostable multivibrator if a second trigger pulse arrives before the first timing period ends?

A: In the standard 555 monostable configuration, if a new trigger pulse arrives before the output pulse period T = 1.1RC has elapsed, the output pulse width remains T regardless of additional trigger pulses during the timing period. The standard circuit is not retriggerable — the 555 will not respond to further triggers until the capacitor has discharged and the output has returned to the stable low state. To implement retriggerable behaviour, additional circuitry is required. - Q: How does the 555 timer achieve precise timing despite being a simple analogue IC?

A: The 555 timer achieves precision through its internal voltage divider, which sets stable threshold voltages at exactly 1/3 Vcc and 2/3 Vcc referenced to the supply voltage. This ratiometric referencing means timing is independent of absolute supply voltage variations (as long as Vcc is stable). The timing is governed by the RC time constanttime constantA measure of how quickly a circuit responds to change. For RC circuits, τ = RC; for RL circuits, τ = L/R. After one time constant, the response reaches ~63% of its final value.. Since both the threshold voltages and the charging voltage scale with Vcc, the timing equations T = 1.1RC (monostable) and T = 0.693RC (astable) depend only on R and C values, not on supply voltage. This makes the 555 inherently stable and predictable for timing applications.

References & Resources (Not Applicable)

This section is not required for this experiment.

Was this experiment helpful?

Your feedback helps us improve

Please Sign In to rate this experiment.