Mathematical Operations with Op-Amps

Running this experiment? Please set the simulation type to Transient / DC Analysis.

Aim

- Summing Amplifier

- Differential Amplifier

- Integrator and Differentiator

- Log and Antilog Amplifiers

Apparatus & Software

| Component | Quantity |

|---|---|

| Function Generator | 1 |

| DC Supply | 3 |

| Oscilloscope | 1 |

| Bread Board | 1 |

| 0.1 µF Capacitor | 1 |

| 10 kΩ Resistor | 4 |

| µA741 Op-Amp | 1 |

| 47 kΩ Resistor | 2 |

Theory

Pre-Lab / Circuit Diagram

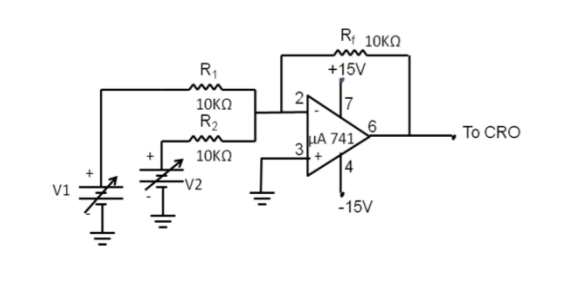

Fig 1: Summing amplifier — µA741, R1 = R2 = Rf = 10 kΩ, supply ±15 V. For weighted sum Vo2 = V1 + 4.7·V2: Rf = 47 kΩ, R1 = 47 kΩ, R2 = 10 kΩ.

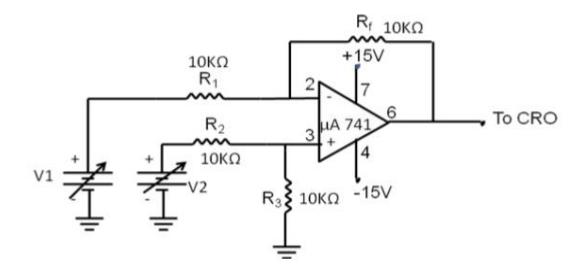

Fig 2: Differential amplifier — µA741, R1 = R2 = Rf = R3 = 10 kΩ, supply ±15 V. Vo = V2 − V1.

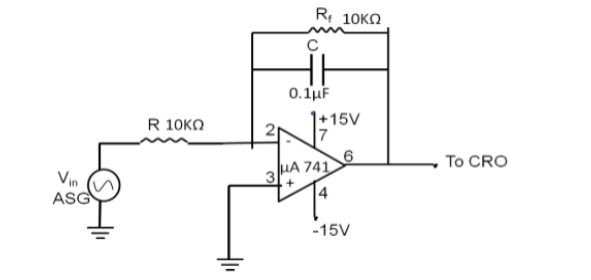

Fig 3: Integrator — µA741, R = 10 kΩ (series input), C = 0.1 µF (feedback), supply ±15 V.

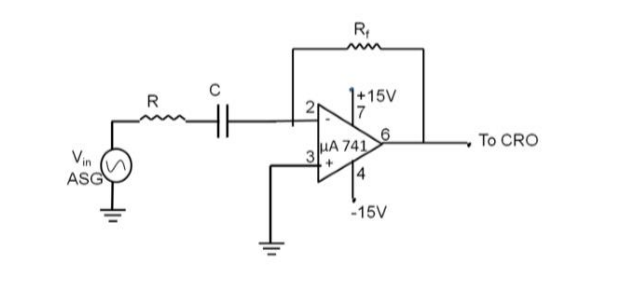

Fig 4: Differentiator — µA741, C at input in series with R, Rf in feedback, supply ±15 V.

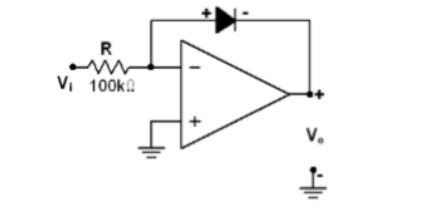

Fig 5: Log amplifier — µA741, R = 100 kΩ series input, diode in feedback path. Vo = −VT·ln(Vi / R·I0).

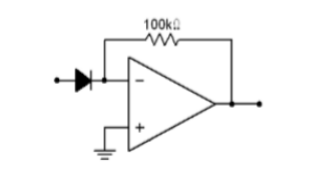

Fig 6: Antilog amplifier — µA741, diode at input, Rf = 100 kΩ in feedback. Vo = −R·Is·e^(Vin/VT).

Procedure

- Connect the summing amplifier circuit (Fig 1) with R1 = R2 = Rf = 10 kΩ. Apply two DC input voltages V1 and V2 and measure Vout = −(V1 + V2) for the combinations given in the observation table.

- Modify the circuit to realise Vo2 = V1 + 4.7·V2 by selecting Rf = 47 kΩ, R1 = 47 kΩ, R2 = 10 kΩ. Measure Vout for the same input combinations and compare with theoretical values.

- Connect the differential amplifier circuit (Fig 2) with R1 = R2 = Rf = R3 = 10 kΩ. Apply two DC voltages and verify Vo3 = V1 − V2 for the combinations in the observation table.

- Connect the integrator circuit (Fig 3) with R = 10 kΩ and C = 0.1 µF. Apply a sine wave (10 kHz, 2 Vpp) and observe the 90° phase-shifted cosine output.

- Apply a square wave (100 Hz, 10 ms period, 2 Vpp) and observe the triangular output. Justify the choice of RC (time constanttime constantA measure of how quickly a circuit responds to change. For RC circuits, τ = RC; for RL circuits, τ = L/R. After one time constant, the response reaches ~63% of its final value. = 10 kΩ × 0.1 µF = 1 ms, much smaller than the 10 ms period). Calculate gain in each case.

- Connect the differentiator circuit (Fig 4). Apply a sine wave (10 kHz, 2 Vpp) and observe the cosine output (note: output is 180° out of phase due to inverting configuration).

- Apply a square wave (100 Hz, 2 Vpp) and observe the impulse-like spikes at each rising and falling edge. Record the output waveform.

- Connect the log amplifier (Fig 5). Set supply to ±12 V. Set Vin = 1 V and record the output voltage across the diode.

- Increase Vin in steps of 1 V up to 20 V. Record output at each step. Plot input-output characteristics.

- Connect the antilog amplifier (Fig 6). Set Vin = 100 mV and record the output across the resistor (note the negative sign).

- Increase Vin in steps of 50 mV up to 500 mV, then larger steps. Record output at each step. Plot input-output characteristics and note the saturation voltage.

Simulation / Execution

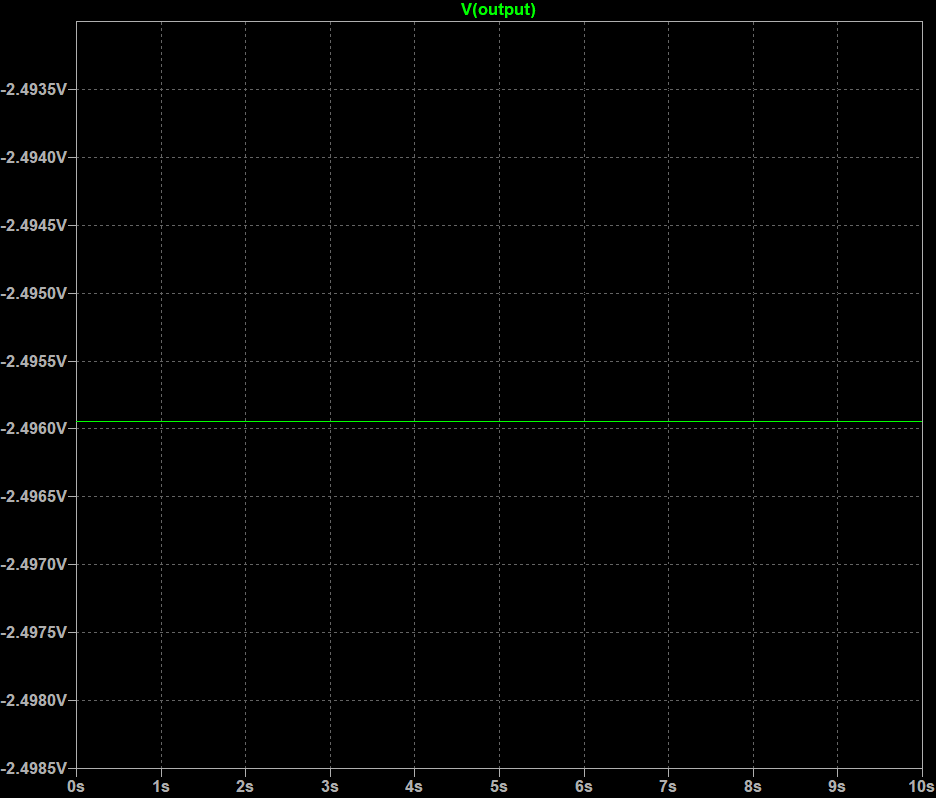

LTspice simulation — Summing amp: V1 = 2 V, V2 = 0.5 V → Vout = −2.4975 V (theoretical: −2.5 V). Flat DC output confirms correct inverting summation.

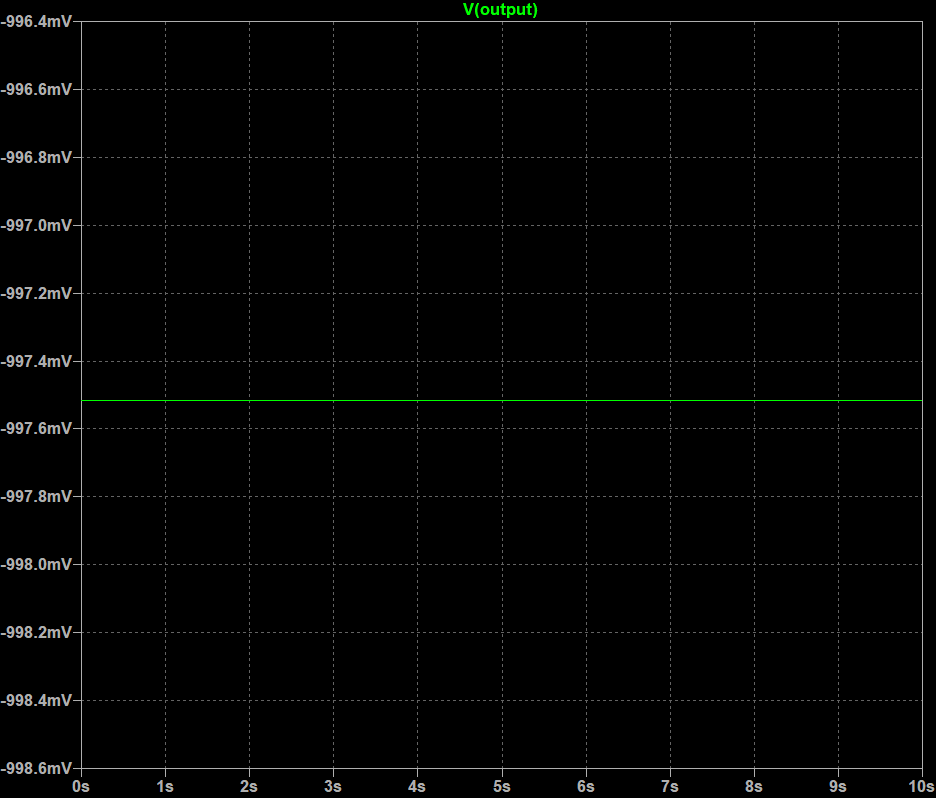

LTspice simulation — Differential amp: V1 = 2 V, V2 = 1 V → Vout = −997.5 mV ≈ −1 V (theoretical: V2 − V1 = −1 V). Confirms subtractor operation.

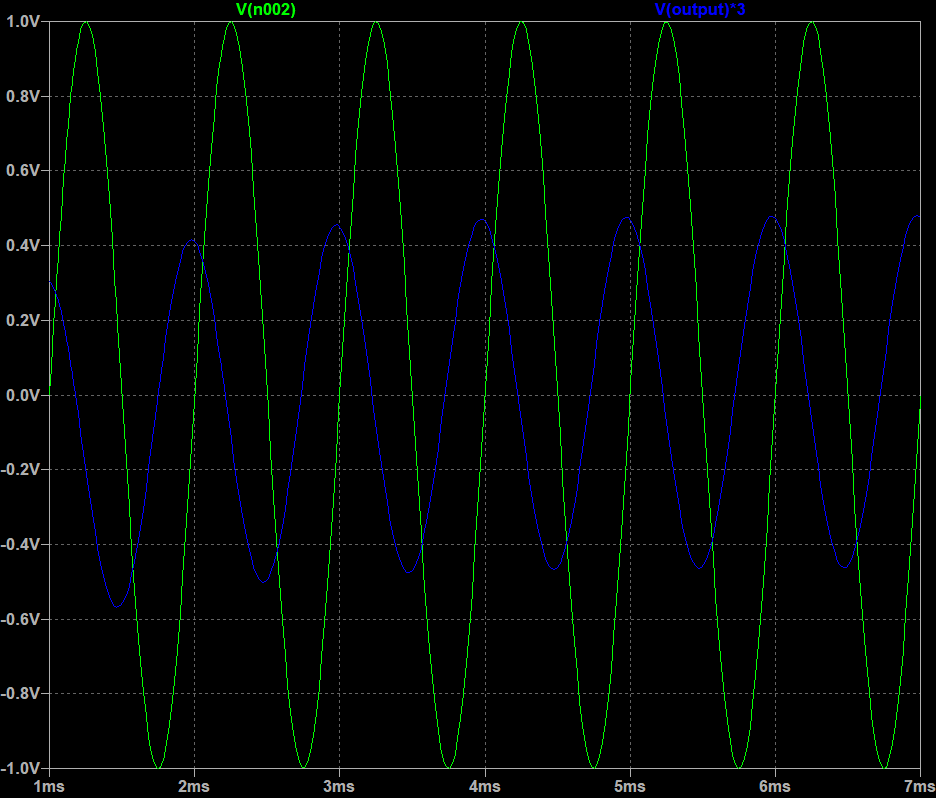

LTspice simulation — Integrator with sine wave input (green, V(n002)): output (blue, V(output)×3, amplified for visibility) is a cosine — 90° phase shift confirms integration. Frequency = ~700 Hz.

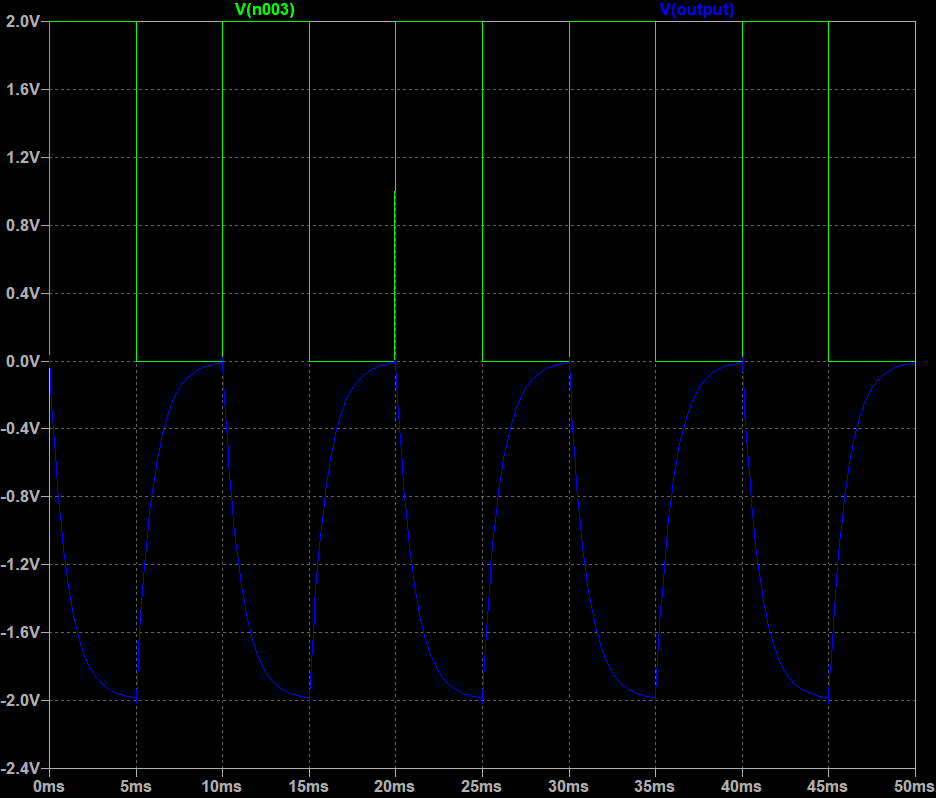

LTspice simulation — Integrator with square wave input (green, V(n003)): output (blue, V(output)) is a triangular wave. Integration of constant = ramp; alternating ramps produce triangle. Period = 10 ms.

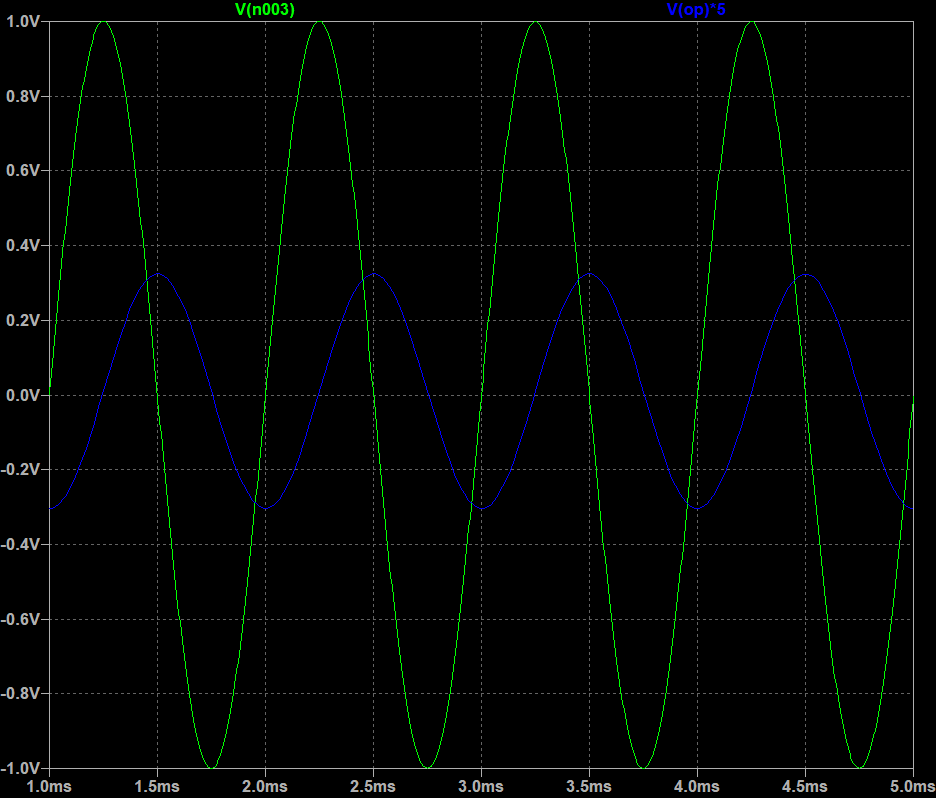

LTspice simulation — Differentiator with sine input (green, V(n003)): output (blue, V(op)×5, amplified) is a cosine — differentiation of sine = cosine. Note 180° phase inversion due to inverting configuration.

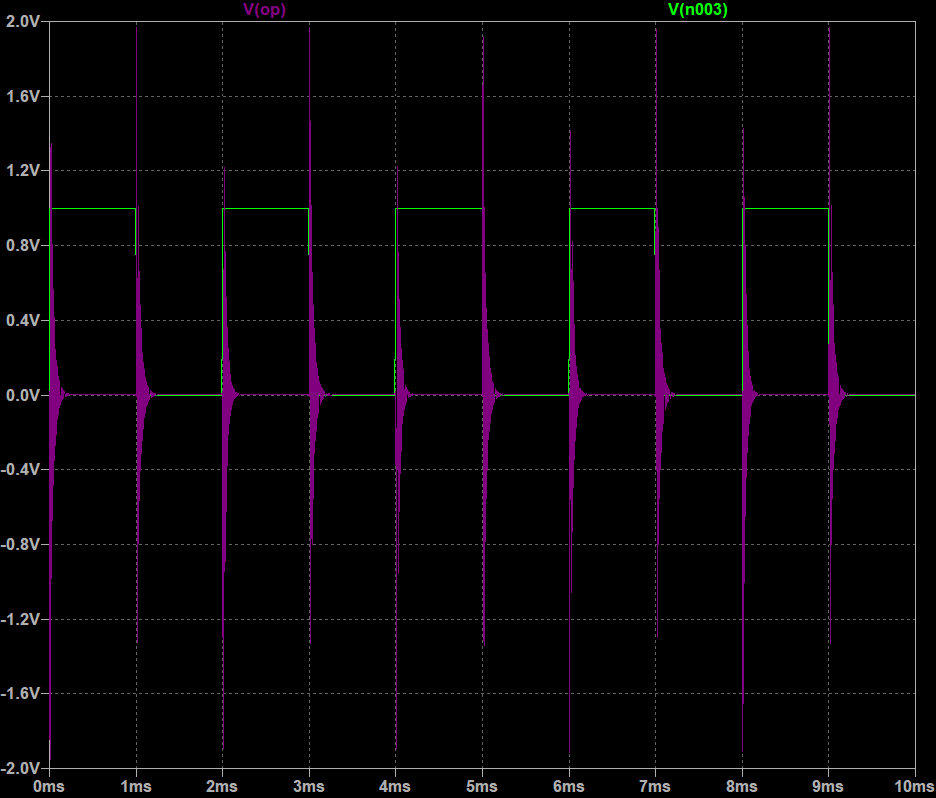

LTspice simulation — Differentiator with square wave input (green, V(n003)): output (magenta, V(op)) shows sharp impulse spikes at each rising and falling edge transition. confirming differentiation of a square wave.

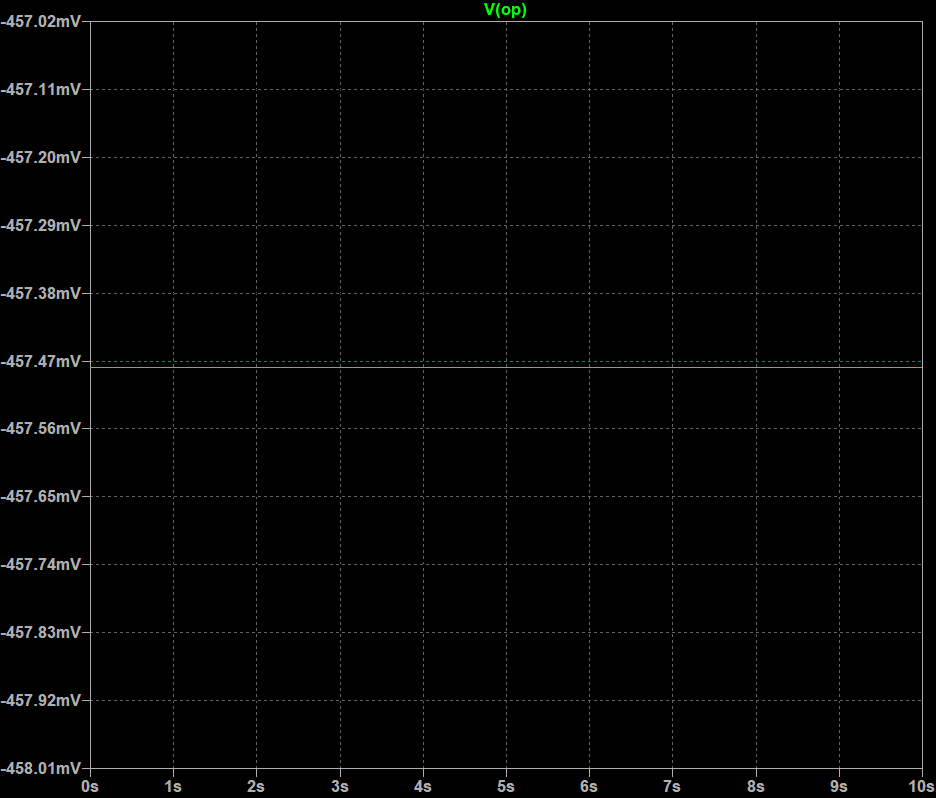

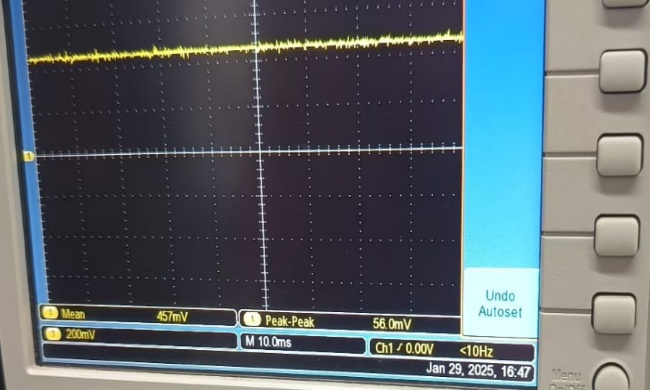

LTspice simulation — Log amp: Vin = 4 V → Vout = −457.47 mV. Flat DC line confirms steady-state log operation. Matches hardware observation of −457 mV at Vin = 4 V.

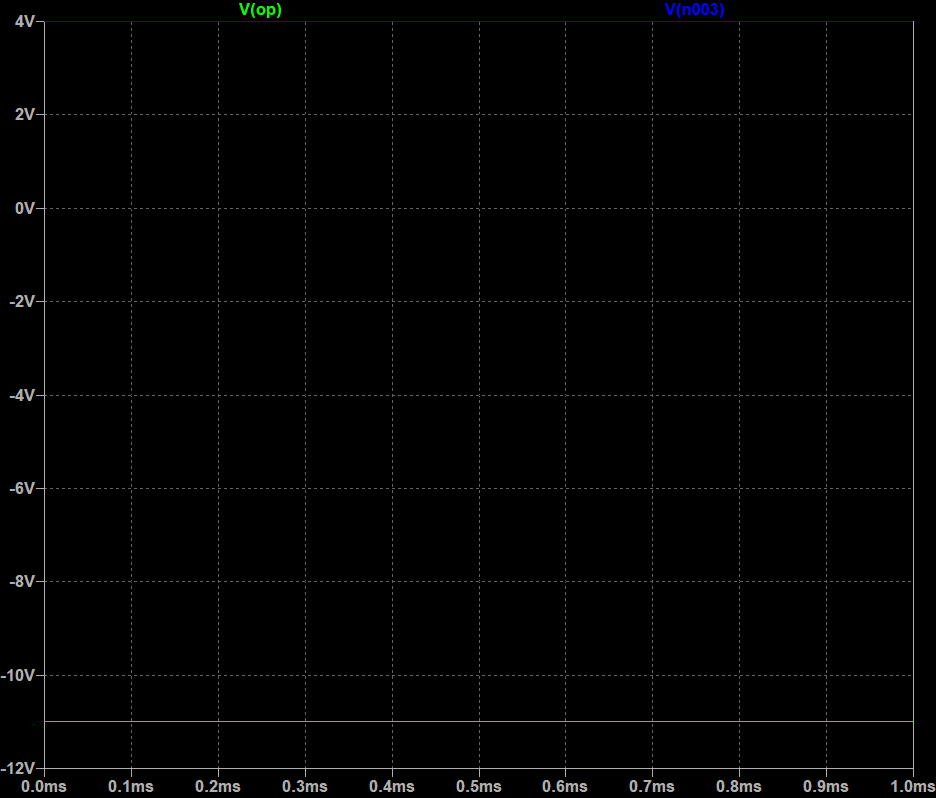

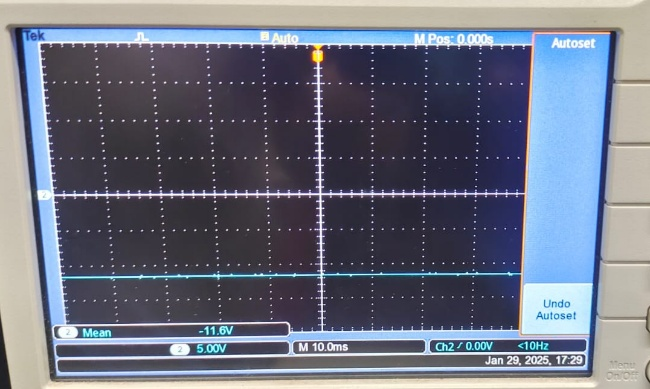

LTspice simulation — Antilog amp: Output V(op) saturates at −11.6 V (green trace, supply-limited) for high input voltage. Input V(n003) shown in blue. Matches hardware saturation observation.

Observations

| V1 (V) | V2 (V) | V01 = −(V1+V2) Measured (V) | V02 = −(V1+4.7V2) Measured (V) |

|---|---|---|---|

| 1 | 1 | -2.07 | -5.73 |

| 2 | 0.5 | -2.56 | -4.37 |

| 1 | 0.2 | -1.25 | -1.94 |

| 2 | 2 | -4.06 | -11.48 |

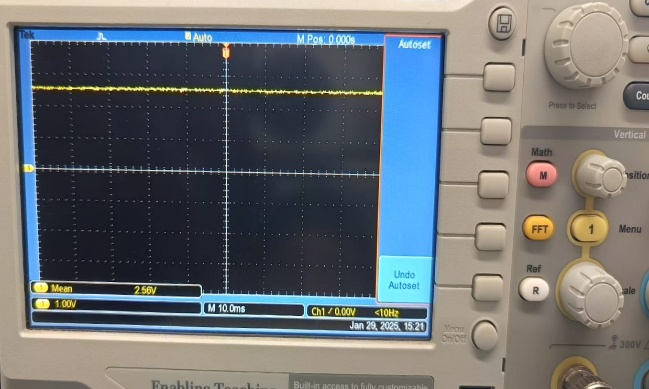

Oscilloscope — Summing amp: Mean = 2.56 V (displayed positive due to probe reversal; actual output = −2.56 V for V1=2, V2=0.5). Confirms correct summation with ~0.06 V error from ideal −2.5 V.

| V1 (V) | V2 (V) | V03 = V1 − V2 Measured |

|---|---|---|

| 2 | 1 | 1.02 V |

| 2 | 0.5 | 1.52 V |

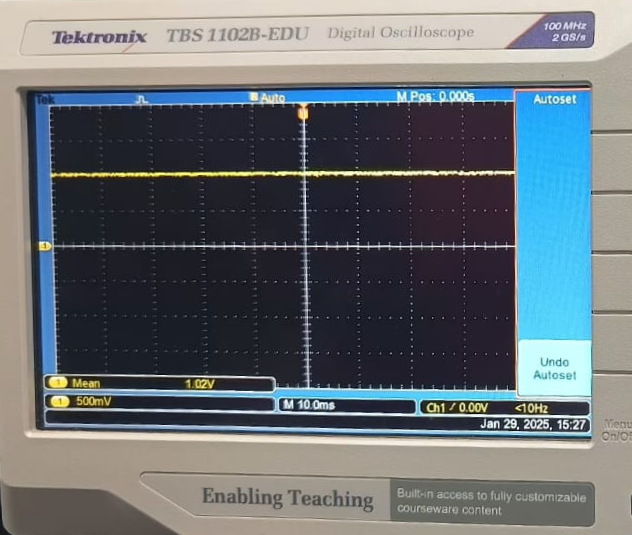

Oscilloscope — Differential amp: Mean = 1.02 V for V1 = 2 V, V2 = 1 V (theoretical: 1 V). Error ≈ 0.02 V, attributed to wire resistance and non-ideal Op-Amp.

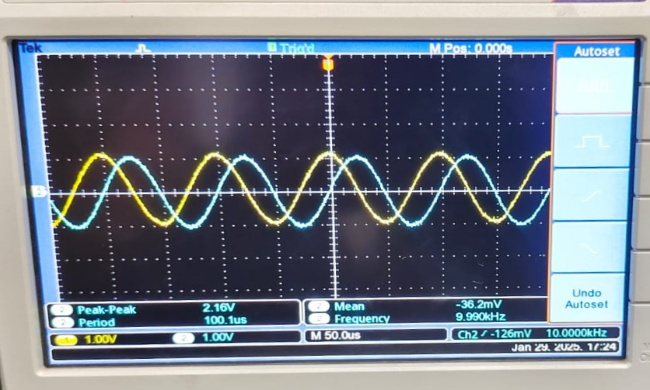

Oscilloscope — Integrator with sine input: yellow = input (Vpp = 2.16 V, 9.99 kHz); cyan = output showing 90° phase-shifted cosine. Confirms integration: ∫sin(ωt)dt = cos(ωt) in inverting mode.

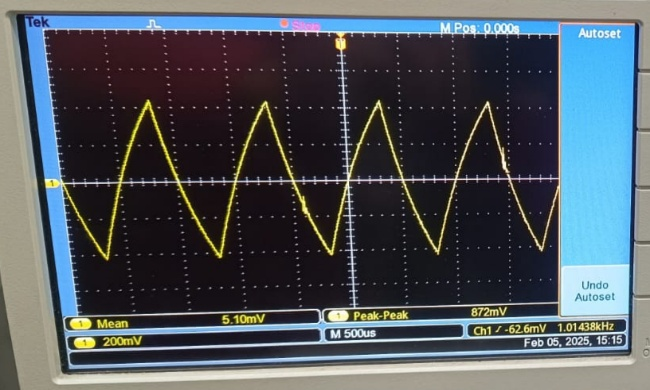

Oscilloscope — Integrator with square wave input: triangular output waveform obtained. Mean = 5.10 mV, Peak-Peak = 872 mV, Freq ≈ 1.01 kHz. Integration of alternating constants yields positive and negative ramps forming a triangle.

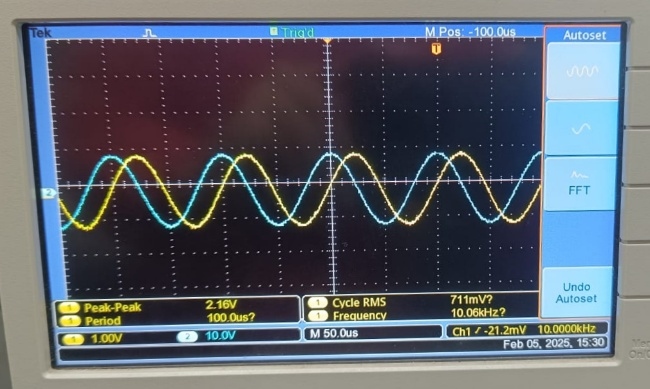

Oscilloscope — Differentiator with sine input: yellow = input (Vpp = 2.16 V, 10.06 kHz); cyan = output showing cosine waveform. The output should be −cosine (inverting differentiator), but appears as +cosine due to reversed probe connection. Simulation confirms correct −cos output.

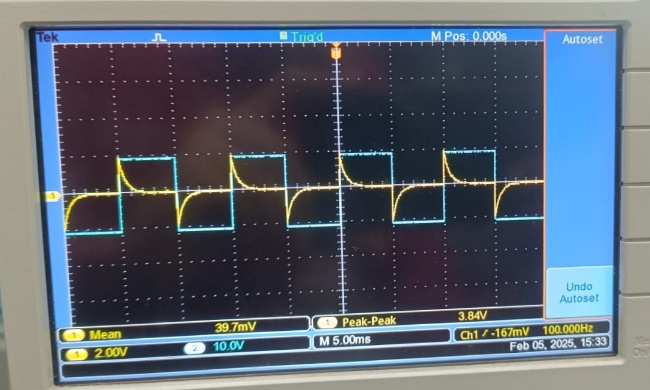

Oscilloscope — Differentiator with square wave input: cyan = input square wave; yellow = output showing sharp positive and negative spikes at every rising and falling edge transition. Mean = 39.7 mV, Peak-Peak = 3.84 V. Confirms differentiation: d/dt of a step = impulse.

| Input Voltage (V) | Output Voltage (mV) |

|---|---|

| 1 | -420 |

| 2 | -431 |

| 3 | -446 |

| 4 | -457 |

| 5 | -467 |

| 6 | -475 |

| 7 | -482 |

| 8 | -488 |

| 9 | -492 |

| 10 | -498 |

| 12 | -502 |

| 14 | -511 |

| 16 | -518 |

| 18 | -522 |

| 20 | -527 |

Oscilloscope — Log amp: Mean = 457 mV displayed (positive due to probe reversal; actual output = −457 mV for Vin = 4 V). Matches LTspice simulation value of −457.47 mV and table entry. Output does not exceed diode breakdown voltage.

| Input Voltage (V) | Output Voltage (V) |

|---|---|

| 0.05 | -0.0023 |

| 0.075 | -0.0154 |

| 0.1 | -0.0158 |

| 0.15 | -0.017 |

| 0.2 | -0.023 |

| 0.25 | -0.0414 |

| 0.3 | -0.1111 |

| 0.35 | -0.37 |

| 0.4 | -1.35 |

| 0.45 | -4.58 |

| 0.5 | -11.5 |

| 0.6 | -11.6 |

| 0.8 | -11.6 |

| 4 | -11.6 |

| 10 | -11.6 |

Oscilloscope — Antilog amp saturation: Mean = −11.6 V (Ch2), confirming output is clamped at the negative supply rail. Supply = ±12 V; Op-Amp output saturates at ≈ −(Vcc − 0.4) = −11.6 V. Matches simulation.

Calculations

Results & Analysis

| Circuit | Expected Behaviour | Observed Behaviour | Error / Notes |

|---|---|---|---|

| Summing (equal weights) | Vout = −(V1+V2) | −2.07 V (for V1=V2=1 V) | ~0.07 V error |

| Summing (weighted) | Vout = −(V1+4.7V2) | −5.73 V (for V1=V2=1 V) | ~0.03 V error |

| Differential | Vout = V1−V2 | 1.02 V (V1=2 V, V2=1 V) | ~0.02 V error |

| Integrator (sine 10 kHz) | 90° phase-shifted cosine | Cosine output confirmed | Probe reversal caused sign flip |

| Integrator (square wave) | Triangular output | Triangular waveform, Vpp=872 mV | — |

| Differentiator (sine 10 kHz) | −cos output (inverting) | Cosine observed (probe reversed) | Simulation confirms −cos |

| Differentiator (square wave) | Impulse spikes at transitions | Spikes observed, Vpp=3.84 V | — |

| Log Amplifier | Logarithmic output, limited by diode | −527 mV at Vin=20 V | Output saturates near diode forward drop |

| Antilog Amplifier | Exponential output, limited by supply | Saturates at −11.6 V | Matches ±12 V supply limit |

- Small errors of ±0.02–0.07 V in summing and differential amplifiers are due to non-ideal Op-Amp offset voltages and component tolerances (typical ±5%).

- The integrator and differentiator correctly transformed waveforms as expected: sine→cosine (90° shift), square→triangle (integrator), square→impulses (differentiator).

- Sign inversions observed in hardware (log amp, integrator, differentiator) are due to reversed oscilloscope probe connections, confirmed by simulation.

- The log amplifierlog amplifierAn op-amp circuit that produces an output voltage proportional to the logarithm of the input voltage, typically using a diode or BJT in the feedback path. output confirmed logarithmic compression of the input, limited by the diode forward voltage characteristics.

- The antilog amplifierantilog amplifierAn op-amp circuit that produces an output proportional to the antilogarithm (exponential) of the input. It is the inverse function of a log amplifier. output saturated at −11.6 V (≈ Vcc − 0.4 V), consistent with Op-Amp output saturation limits for a ±12 V supply.

Conclusion

Post-Lab / Viva Voce

- Q: What is a virtual ground in an inverting Op-Amp configuration, and why does it occur?

A: Virtual ground is the condition where the inverting input (−) is at 0 V (same as the grounded non-inverting input), even though it is not physically connected to ground. This occurs because the Op-Amp's very high open-loop gain forces the feedback network to make both inputs equal. For the non-inverting input at 0 V, the feedback drives the inverting input to ≈ 0 V. While no current flows into the high-impedance input, current flows through the input and feedback resistors as if the node were grounded — hence the term 'virtual' ground. - Q: How does changing the feedback resistor Rf in a summing amplifier affect the output?

A: In the inverting summing amplifier, Vout = −Rf(V1/R1 + V2/R2). Increasing Rf increases the gain on all inputs, scaling up the sum. When Rf ≠ R1 or Rf ≠ R2, different weights are assigned (weighted summing). For example, Rf = 47 kΩ with R2 = 10 kΩ gives coefficient 4.7 to V2. Rf controls overall scaling; individual input resistors control relative weighting. - Q: What input-output relationships are observed for the integrator with sine and square wave inputs?

A: For sine input Vin = A sin(ωt): Vout = −(1/RC)∫A sin(ωt)dt = (A/ωRC)cos(ωt) — a cosine (90° phase shift). Since the Op-Amp is inverting, the − sign cancels and the output is +cos. For a square wave input, ∫constant dt = ramp. As the square alternates ±V, the output alternates between positive and negative ramps, producing a triangular waveform. The RC time constant must be much smaller than the input period for proper triangular output. - Q: Why does the output of an antilog amplifier saturate at a voltage close to the supply voltage?

A: The antilog output grows exponentially: Vout = −R·Is·e^(Vin/VT). As Vin increases, the exponential demand exceeds the Op-Amp's physical output capability — the output is limited by the power supply rails (Vcc − 1 to 2 V). In this experiment (±12 V supply), the saturation occurs at ≈ −11.6 V (= −(12 − 0.4) V). Any further increase in Vin cannot increase the output beyond this clamped level. - Q: What is the key difference between an ideal differentiator and an ideal integrator in terms of frequency response?

A: The ideal integrator has transfer function H(s) = −1/(RCs), meaning gain ∝ 1/f — it is a low-pass filter that attenuates high frequencies. The ideal differentiator has H(s) = −RCs, meaning gain ∝ f — it is a high-pass filter that amplifies high-frequency noise. In practice, a resistor is added in series with the input capacitor of the differentiator to limit high-frequency gain and improve stability. - Q: Why is a log amplifier useful in signal processing applications?

A: Log amplifiers compress large dynamic ranges into a smaller manageable range, since Vout ∝ ln(Vin). Signals varying over several orders of magnitude are mapped to a small output range. Applications include: audio processing (human hearing is logarithmic), radar/sonar signal processing, measurement instruments handling wide-range signals, and as building blocks for analog multiplication (log A + log B = log AB) using summing amplifiers followed by an antilog stage. - Q: What causes errors in a differential amplifier, and how can they be minimised?

A: Error sources: (1) Resistor mismatches — unequal R1, R2, R3, Rf cause incomplete common-mode cancellation, producing a finite output when V1 = V2 (as seen: 13.7 mV instead of 0 V). (2) Op-Amp input offset voltage — inherent DC error amplified to the output. (3) Bias current imbalance — unequal currents at ± inputs add offset. Minimisation: use precision resistors (0.1% tolerance), Op-Amps with low offset voltage (e.g., OP07), and add trimming potentiometers to null residual offset.

References & Resources (Not Applicable)

This section is not required for this experiment.

Was this experiment helpful?

Your feedback helps us improve

Please Sign In to rate this experiment.