Hardware-Oriented

Design and Implementation of Full Subtractor Circuit on FPGA Board

Aim

To design and implement a full subtractor circuit on the FPGAfpgaField-Programmable Gate Array — an integrated circuit containing configurable logic blocks and programmable interconnects that can be reconfigured after manufacturing to implement custom digital circuits. board.

Apparatus & Software

| S.No. | Tool / Equipment | Purpose |

|---|---|---|

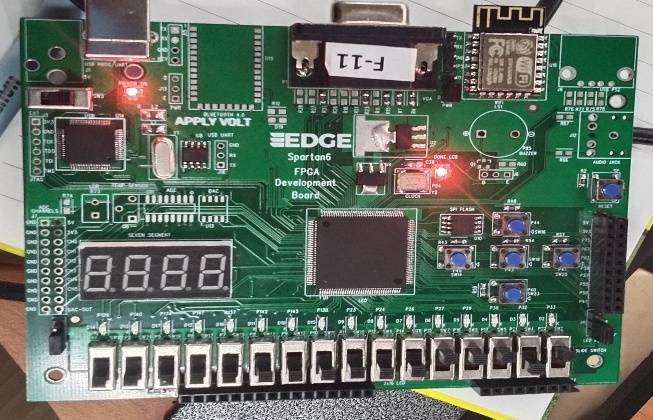

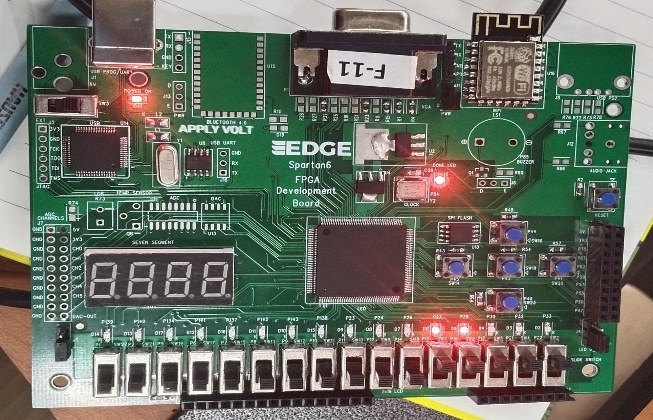

| 1 | FPGA Development Board (Spartan-6) | Hardware implementation and verification |

| 2 | Xilinx ISE Software | HDL design entry, synthesis, and implementation |

| 3 | ISim Simulator | Functional simulation before hardware download |

| 4 | USB Programming Cable | Downloading bitstream to FPGA board |

| 5 | PC / Workstation | Running the Xilinx software environment |

Theory

A full subtractor is a combinational circuit that performs the subtraction of two 1-bit binary numbers while also taking into account a borrow-in bit from the previous bit position. It has three inputs: A (minuend), B (subtrahend), and Bin (borrow-in), and two outputs: Difference (D) and Borrow-out (Bout).

The Difference output is high when an odd number of inputs are high, which is identical to the XOR of all three inputs — the same expression as the Sum in a full adder. The Borrow-out is high when the minuend A is smaller than the effective subtrahend (B + Bin), indicating that a borrow must be taken from the next higher bit position.

The Boolean expressions for Difference and Borrow are:

The truth table for a full subtractor is given below:

| A | B | Bin | Difference | Bout |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Pre-Lab / Circuit Diagram (Not Applicable)

This section is not required for this experiment.

Procedure

- Open Xilinx ISE and create a new project targeting the appropriate FPGA device.

- Create a new Verilog source file and write the full subtractor module using the assign statement for Difference (XOR of all inputs) and Borrow (using AND-OR with complements).

- Create the User Constraints File (UCF) mapping the three input ports (a, b, c) and two output ports (Difference, Borrow) to the designated FPGA pin locations.

- Hardware Layout: Map `a` (minuend), `b` (subtrahend), `c` (borrow-in) to the toggle switches and `Difference`, `Borrow` to the LEDs.

- Run the behavioural simulation in ISim by applying all 8 input combinations and verifying the outputs match the truth table.

- Synthesize and implement the design in Xilinx ISE.

- Generate the programming bitstreambitstreamThe binary configuration file downloaded to an FPGA that programs its internal logic blocks and routing interconnects to implement a specific design. and download to the FPGA board.

- Test all six representative input combination cases using the toggle switches and observe the LED outputs.

Simulation / Execution

Verilog Code for Full Subtractor Implementation:

verilog

module FullSubtractor(

input a,

input b,

input c,

output Difference,

output Borrow

);

assign Difference = a ^ b ^ c;

assign Borrow = ((~a) & b) | (b & c) | (c & (~a));

endmoduleUser Constraints File for Full Subtractor:

properties

NET "a" LOC = "P22";

NET "b" LOC = "P21";

NET "c" LOC = "P17";

NET "Difference" LOC = "P29";

NET "Borrow" LOC = "P27";Note: The input c in the code represents the borrow-in (Bin). The Difference is computed using triple XOR, identical to the Sum in a full adder. The Borrow is computed using the complement of A with AND-OR expressions reflecting when a borrow must be generated.

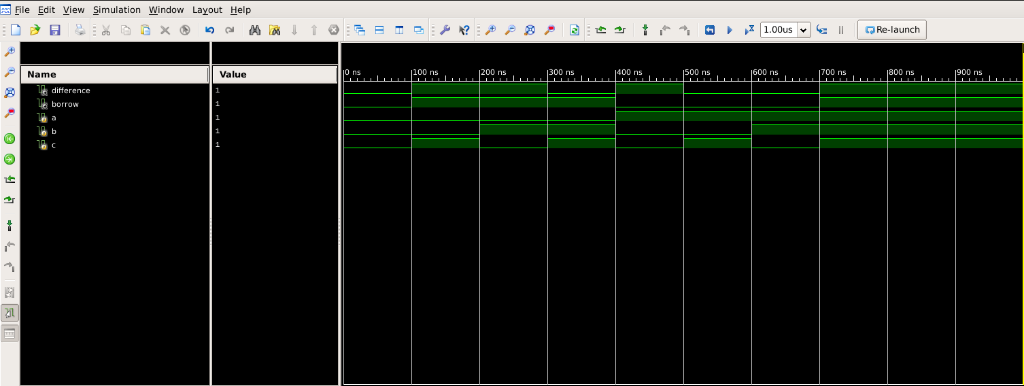

Simulation waveform for Full Subtractor: outputs Difference and Borrow match the truth table for all 8 input combinations.

From the simulation waveform, the outputs Difference and Borrow exactly match the truth table. Borrow is high only when the minuend A is smaller than the effective subtrahend (B + Bin). When all inputs are 1, both outputs are also 1.

Observations

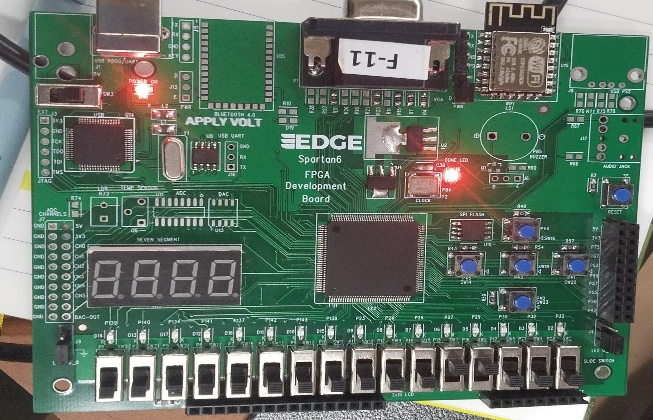

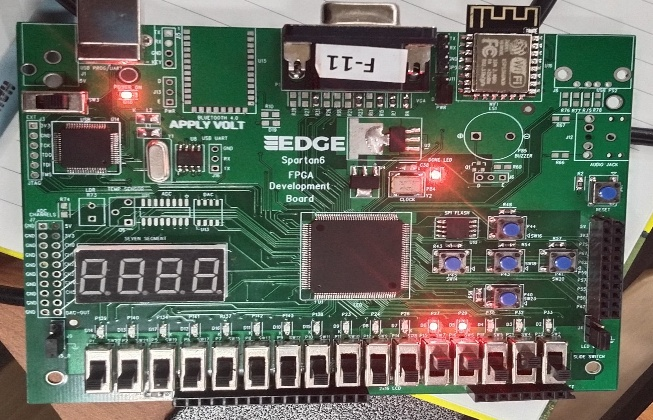

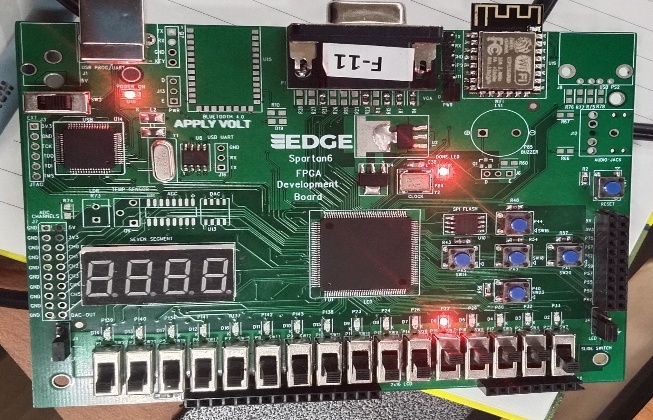

Hardware implementation was verified on the FPGA board. The following 6 representative cases were successfully captured and verified against the truth table.

| Input (A B Bin) | Difference (Obs.) | Bout (Obs.) | Expected Diff. | Expected Bout | Status |

|---|---|---|---|---|---|

| 0 0 0 | 0 | 0 | 0 | 0 | Verified |

| 0 1 0 | 1 | 1 | 1 | 1 | Verified |

| 0 1 1 | 0 | 1 | 0 | 1 | Verified |

| 1 0 0 | 1 | 0 | 1 | 0 | Verified |

| 1 0 1 | 0 | 0 | 0 | 0 | Verified |

| 1 1 1 | 1 | 1 | 1 | 1 | Verified |

Input 000: Difference=0, Bout=0

Input 010: Difference=1, Bout=1

Input 011: Difference=0, Bout=1

Input 100: Difference=1, Bout=0

Input 101: Difference=0, Bout=0

Input 111: Difference=1, Bout=1

Calculations

Verification of Boolean expressions for representative test cases:

| A | B | Bin | Difference | Bout |

|---|---|---|---|---|

| 0 | 0 | 0 | 0⊕0⊕0 = 0 | (1·0)+(0·0)+(0·1) = 0 |

| 0 | 1 | 1 | 0⊕1⊕1 = 0 | (1·1)+(1·1)+(1·1) = 1 |

| 1 | 0 | 0 | 1⊕0⊕0 = 1 | (0·0)+(0·0)+(0·0) = 0 |

| 1 | 1 | 1 | 1⊕1⊕1 = 1 | (0·1)+(1·1)+(1·0) = 1 |

Results & Analysis

The Full Subtractor experiment provided the following insights:

- Implementation Verification: The Verilog module using `assign` statements was successfully synthesized and downloaded to the FPGA.

- Truth Table Validation: All 8 input combinations were verified in simulation. The hardware test cases confirmed that the Difference output follows the XOR parity logic (similar to Full Adder Sum) and the Borrow output is generated correctly whenever the subtrahend exceeds the minuend.

- Subtraction Logic: The experiment highlighted the role of the borrow bit in cascading subtraction operations across multiple bits.

Conclusion

In this experiment, the implementation of a full subtractor on the FPGA board was successfully completed. Both software simulation and hardware implementation were performed and verified against the respective truth table. Different cases that produce similar output combinations were identified. The experiment demonstrates that the Difference output expression is identical to that of the full adder Sum, while the Borrow expression uses the complement of the minuend A — highlighting the structural relationship between addition and subtraction in combinational arithmetic circuits.

Post-Lab / Viva Voce

- Q: What is the difference between a half subtractor and a full subtractor?

A: Half subtractor handles 2 inputs (A, B) and no borrow-in. Full subtractor handles 3 inputs (A, B, Bin) to support multi-bit cascading. - Q: Why is the Difference expression in a full subtractor identical to the Sum expression in a full adder?

A: Both use XOR logic (odd parity) for the result bit. The difference lies only in the carry/borrow generation logic. - Q: When does Borrow-out become high?

A: When Minuend < Subtrahend (effectively). Boolean: `Bout = (~A&B) | (B&Bin) | (Bin&~A)`. - Q: How is subtraction typically done in processors?

A: Using 2's complement addition. A - B is equal to A + (~B + 1). This allows the same Adder hardware to perform subtraction. - Q: Comparison of Adder vs Subtractor Truth Tables?

A: Sum and Difference columns are identical. Carry and Borrow columns differ based on the majority vs borrowing logic.

References & Resources

Digital Electronics Lab Manual

Download Common Lab Manual (PDF)

Download Common Lab Manual (PDF)

Was this experiment helpful?

Your feedback helps us improve

Please Sign In to rate this experiment.